# Current Starved VCO Verses Source Coupled VCO for PLL in 180nm CMOS Technology

<sup>1.</sup>Shubham Durge <sup>2.</sup>Prof.Ashish Manusmare

**Abstract:** This paper is about performance comparison of Current Starved VCO and Source Coupled VCO for Phase Lock Loop. The comparison is based on 180nm CMOS technology and based on different measuring parameter. The design is being built on Tanner environment tool with a high oscillation frequency, low power consumption, and low area. Simulation results are illustrated that area and power consumption in Current Starved VCO verses Source Coupled VCO with wide frequency range. This design procedure is very efficient for Phase Lock Loop.

*Keywords:* Voltage Control Oscillator (VCO), Current Starved VCO, Source Coupled VCO, Phase Look Loop, CMOS, Area (W/L ratio), Power.

Date of Submission: 26-08-2018

Date of acceptance: 11-09-2018

## I. Introduction

A CMOS voltage control oscillator (VCO) is a block which has been critically used in Phase Lock Loop (PLL), which are designed for low power consumption and area occupied by the PLL must be less. VCO is commonly associate with RF Transceiver in signal processing tasks like signal generation and frequency selection. So PLL is less accurate in RF Transceiver in feedback loop, whose frequency can be control with the help of VCO control signal.

A VCO plays a vital role in communication system, providing a periodic signal required for digital circuit and also a frequency transmission in digital circuit. Their output frequency is a function of control input voltage. An ideal VCO is a circuit whose output frequency is a linear function of its control voltage. Most of the application as required a variable control input voltage as they required different frequency. There are two category of Voltage control oscillator viz. Current Starved VCO and Source coupled VCO.

#### 1.1 Current Starved VCO

## **II.** Circuit Description

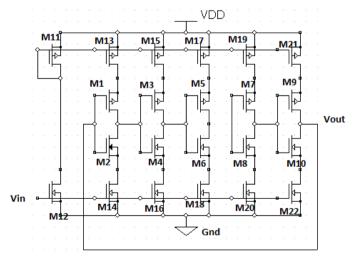

The schematic operation of current starved VCO is similar to Ring oscillator. Figure-1 shows the five stages Current Starved VCO. PMOSM1 and NMOSM2 is an Inverter, while PMOSM13 and NMOSM14 operate as a current source. We also say's the inverter starved for current. The current in the first NMOS and PMOS are mirrored in each inverter/current source stage. PMOSM11 and NMOSM11 drain currents are the same and are set by the input control voltage.

Figure-1: Current Starved Voltage controlled oscillator

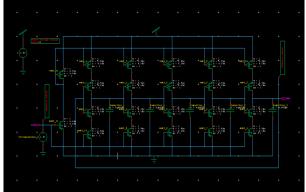

The design of Current starved VCO for five stages is shown in below figure-2

Figure-2: Design implementation of Current starved VCO

The size for figure 2 is being calculated as a total capacitance. The total capacitance  $C_T$  is given by formula,

$$C_T = \frac{\left[\mathbb{N} \times C_o(W_P L_P + W_N L_N)\right]}{2}$$

VCVE

Where,

$C_o$  is oxide capacitance N is the number of cascade inverter The drain current ( $I_D$ ) is calculated as

The oscillation frequency is given by,

$$F = \frac{1}{N \times T_D}$$

Where,  $T_D$  is delay time.

#### 1.2 Source Coupled VCO

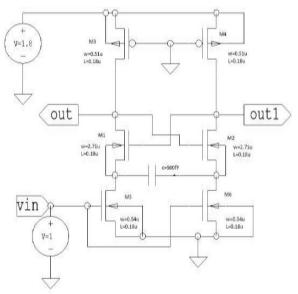

The operation of the CMOS source coupled VCO in figure-3. The Load MOSFETs M3 and M4 help to pull the output. The MOSFETs M5 and M6 behave as constant-current source sinking a current Id. MOSFETs M1 and M2 act as switches. MOSFET M1 is OFF and M2 is ON switch, because the voltage of terminal Out1 is larger than voltage of terminal Out. Therefore current through MOSFET M2 is two times Id and the capacitor will be charged byId current, because of constant current source M6 sinking current Id. When the voltage plate-1 and plate-2 of capacitor terminal is same then capacitor say's fully charged. The current Id through Capacitor causesplate-1 to discharge down through ground. When plate-1 of capacitor is get down, M1 turn ON and M2 turns OFF.

Figure-3 Schematic of Source coupled VCO

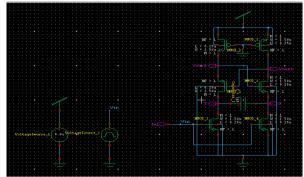

Figure-4shows the designed single stage Source Coupled VCO.

The voltage atplate-1 changed before switching take place the time it takes plate-1 to changes 2Vth is given by  $C \times 2Vth$

$$\Delta t = \frac{C \times 2VU}{Id}$$

Since the circuit is symmetrical two of these discharge time are needed for each cycle of oscillator the frequency ofoscillations is given by

$$Fosc = \frac{1}{2 \Delta t}$$

## **III. Simulation Results**

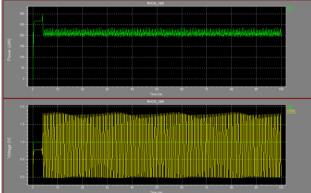

Simulation of Current starved VCO When the output of charge pump is applied to VCO as a control signal the respective output waveform is as shown in figure-3. It seen that the 1.683 GHz output frequency is generated for 1.0 V control voltage.

Figure-5: Output waveform of Current Starved VCO

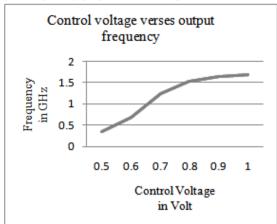

The output waveform of current starved VCO for control voltage 1.0V generates an output frequency of 1.683 GHz as shown in figure-3. The simulation results for Average power consumption for figure-2 is calculate in Tanner T-Spice is 2.1288e-004 Watt. When the control voltage is varying continuously form 0.5V to 1.0V the oscillation frequency is varying from 342.4 MHz to 1.683 GHz respectively as shown in table 1.

| Table 1. Control voltage verses output frequency. |                           |                          |  |

|---------------------------------------------------|---------------------------|--------------------------|--|

| Sr.<br>No.                                        | Control Voltage<br>(Volt) | Output Frequency<br>(Hz) |  |

| 1.                                                | 0.5                       | 342.421 MHz              |  |

| 2.                                                | 0.6                       | 675.675 MHz              |  |

| 3.                                                | 0.7                       | 1.244 GHz                |  |

| 4.                                                | 0.8                       | 1.532 GHz                |  |

| 5.                                                | 0.9                       | 1.638 GHz                |  |

| 6.                                                | 1.0                       | 1.683 GHz                |  |

Table 1: Control voltage Verses output frequency.

The Control voltage verses output frequency graph shown in figure-5.

Figure 5: Graphical representation of Control voltage verses output frequency

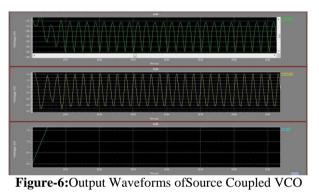

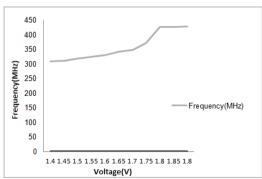

When we applied control voltage 1.4V to 1.8V variable, the Oscillation frequency of the designed source coupled VCO ranges from 307.69 MHz to 425.53 MHz, When we apply control voltage below 1.4V source coupled VCO generates non-linear oscillations. Table II gives the characteristics of the source coupled VCO i.e. control voltage (V) Verses frequency (MHz).

| Sr. No. | Voltage(Volt) | Frequency(MHz) |

|---------|---------------|----------------|

| 1.      | 1.4           | 307.69         |

| 2.      | 1.5           | 318.47         |

| 3.      | 1.6           | 330.03         |

| 4.      | 1.7           | 347.22         |

| 5.      | 1.8           | 425.53         |

Table II: Control Voltage verses Frequency

Figure-7Frequency (MHz) Verses Control Voltage (Volt)

## **IV. Performance Comparison**

In this section, we predict major performances of both VCO's such as input tuning range, range of oscillation frequency, and area and power consumption on qualitative discussion by an analytical approach. Table III shows the performance comparison of both current starved VCO and source coupled VCO. We use the minimum channel length and width of the device. Thus it can be seen that through both VCO's we can achieve minimum area with wide tuning frequency range for PLL. Also the power consumption in Current Starved VCO is reduced as compared to Source Coupled VCO.

| Parameters                     | Current<br>Starved VCO  | Coupled VCO              |

|--------------------------------|-------------------------|--------------------------|

| Technology                     | 0.18µm                  | 0.18µm                   |

| I/P Tuning Range               | 0.5 - 1.0 volt          | 1.4-1.8V                 |

| Range of Oscillation Frequency | 342.421MHz to 1.683 GHz | 307.69 MHz to 427.35 MHz |

| Area                           |                         | 75.9μm <sup>2</sup>      |

| Power Consumption              | 2.1288e-004 Watt        | 6.69mW                   |

Table III Measurement Performance

#### V. Conclusion

This paper differ the performance parameters of two VCO's for PLLs, a current starved VCO and a source coupled VCO withthe schematic design experimentation and with the qualitative evaluation. Our measurement results show that in chip area, powerconsumption and tunable frequency range, a RC based Current starved VCO is superior to a Source Coupled VCO.Also the relative performance difference between ring VCO and LC VCO will be almost constant in the future.Power consumption and chip area of both PLLs will decrease proportional to the technology node. However, noisecharacteristics will get worse inversely proportional to the technology node. The techniques proposed in this paper can also be applied to other low voltage analog and RF circuits to improve their performance.

#### References

- [1]. Dongmin Park, et al, —Design techniques for low voltage VCO with wide tuning range and low sensitivity to environmental variationsl, in IEEE Transaction on Microwave Theory and Techniques, vol. 57, no. 4, April 2009, pp 767 774.

- [2]. Akima, H.; Dec, A.; Suyama, K.- A wide tuning 1.3 GHz LC VCO with fast settling noise filtering voltage regulator in 0.18 μm CMOSprocess, in IEEE Transaction on Microwave Theory and Techniques, 2010, pp 333-336

- [3]. Bodhisatwa Sadhu, Member, IEEE, Mark A. Ferriss, Arun S. Natarajan, SonerYaldiz, Member, IEEE, Jean-Olivier Plouchart, Senior Member, IEEE, Alexander V. Rylyakov, Alberto Valdes-Garcia, Benjamin D. Parker, Aydin Babakhani, Scott Reynolds, Xin Li, Senior Member, IEEE, Larry Pileggi, Fellow, IEEE, Ramesh Harjani, Fellow, IEEE, José A. Tierno, and Daniel Friedman, Member, IEEEA ---Linearized, Low-Phase-Noise VCO-Based 25-GHz PLL with Autonomic Biasing, VOL. 48, NO. 5, MAY 2013

- [4]. Luciano Severino de Paula, Eric Fabris, Sergio Bampi, AltamiroAmadeuSusin, A High Swing Low Power CMOS Differential Voltage-Controlled Ring Oscillatorlin 2007 IEEE Computer Society Annual Symposium on VLSI(ISVLSI'07)

- [5]. Sang\_yeop Lee, ShuheiAmakawa, Noboru Ishihara, and Kazuya Masu, I Low-Phase-Noise Wide-Frequency-Range Ring-VCO-Based Scalable PLL with Subharmonic Injection Locking in 0.18 μm CMOSI, in IEEE 2010.

- [6]. To-Po Wang, —A k-band low power colpitts VCO with voltage to current positive feedback network in 0.18 μm CMOS,I in IEEE on Microwave and Wireless Components Letters, vol. 21, no. 4, April 2011, pp 218 220.

- [7]. HaripriyaJanardhan, Mahmoud FawzyWagdy, —Design of a 1GHz Digital PLL Using 0.18µm CMOS Technologyl in IEEE 2006 Third International Conference on Information Technology: New Generations (ITNG'06)

- [8]. B .Razvi, Design of ANALOG CMOS Integrated Circuits, McGraw-Hill, 2001

- [9]. Nikolay T. Tchamov, Svetozar S. Broussev, IDual-Band LC VCO Architecture With a Fourth-Order Resonatorl in IEEE Transactions on circuits and systems—II: Express Briefs, vol. 54, no. 3, March 2007.

- [10]. Guochi Huang, Student Member, IEEE, and Byung-Sung Kim, Member, IEEE, "Low Phase Noise Self-Switched Biasing CMOS LC Quadrature VCOI in IEEE Transactions on Microwave Theory and Techniques, vol. 57, no. 2, February2009.

Shubham Durge " Current Starved VCO Verses Source Coupled VCO for PLL in 180nm CMOS Technology." IOSR Journal of Environmental Science, Toxicology and Food Technology (IOSR-JESTFT) 12.9 (2018): 87-91.

DOI: 10.9790/2402-1209028791